2.4.5 库和程序包

库和程序包是VHDL的设计共享资源,一些共用的、经过验证的模块放在程序包中,实现代码重用。一个或多个程序包可以预编译到一个库中,使用起来更为方便。

1.库(Library)

库是经编译后的数据的集合,用来存放程序包定义、实体定义、结构体定义和配置定义,使设计者可以共享已经编译过的设计结果。在VHDL语言中,库的说明总是放在设计单元的最前面:

LIBRARY库名;

这样在设计单元内的语句就可以使用库中的数据。VHDL语言允许存在多个不同的库,但各个库之间是彼此独立的,不能互相嵌套。常用的库如下:

(1)STD库

逻辑名为STD的库为所有设计单元隐含定义,即“LIBRARY STD;”子句隐含存在于任意设计单元之前,而无须显式写出。

STD库包含预定义程序包STANDARD与TEXTIO。

(2)WORK库

逻辑名为WORK的库为所有设计单元隐含定义,用户不必显式写出“LIBRARY WORK;”。同时设计者所描述的VHDL语句不须作任何说明,都将存放在WORK库中。

(3)IEEE库

最常用的库是IEEE。IEEE库中包含IEEE标准的程序包,包括STD_LOGIC_1164、NUMERIC_STD_LOGIC、NUMERIC_STD以及其他一些程序包。其中STD_LOGIC_1164是最主要的程序包,大部分可用于可编程逻辑器件的程序包都以这个程序包为基础。

(4)用户定义库

用户为自身设计需要所开发的共用程序包和实体等,也可汇集在一起定义成一个库,这就是用户库,在使用时同样需要说明库名。

2.程序包(Package)

程序包说明像C语言中的include语句一样,用来罗列VHDL语言中所要用到的常数定义、数据类型、函数定义等,是一个可编译的设计单元,也是库结构中的一个层次。要使用程序包时可用USE语句说明,例如:

程序包由标题和包体两部分组成,其结构如下:

标题是主设计单元,它可以独立编译并插入设计库中。包体是次级设计单元,它可以在其对应的标题编译并插入设计库之后,再独立进行编译并也插入设计库中。

包体并不总是需要的。但在程序包中若包含有子程序说明时则必须用对应的包体。这种情况下,子程序体不能出现在标题中,而必须放在包体中。若程序包只包含类型说明,则包体是不需要的。

常用的程序包如下:

(1)STANDARD程序包

STANDARD程序包预先在STD库中编译,此程序包中定义了若干类型、子类型和函数。IEEE1076标准规定,在所有VHDL程序的开头隐含有下面的语句:

LIBRARY WORK.STD;

USE STD.STANDARD.ALL;

因此不需要在程序中使用上面的语句。

(2)STD_LOGIC_1164程序包

STD_LOGIC_1164预先编译在IEEE库中,是IEEE的标准程序包,其中定义了一些常用的数据和子程序。

此程序包定义的数据类型STD_LOGIC、STD_LOGIC_VECTOR以及一些逻辑运算符都是最常用的,许多EDA厂商的程序包都以它为基础。

(3)STD_LOGIC_UNSIGNED程序包

STD_LOGIC_UNSIGNED程序包预先编译在IEEE库中,是Synopsys公司的程序包。此程序包重载了可用于INTEGER、STD_LOGIC和STD_LOGIC_VECTOR三种数据类型混合运算的运算符,并定义了一个由STD_LOGIC_VECTOR型到INTEGER型的转换函数。

(4)STD_LOGIC_SIGNED程序包

STD_LOGIC_SIGNED程序包与STD_LOGIC_UNSIGNED程序包类似,只是STD_LOGIC_SIGNED中定义的运算符考虑到了符号,是有符号的运算。

下面是一自定义程序包的例子:

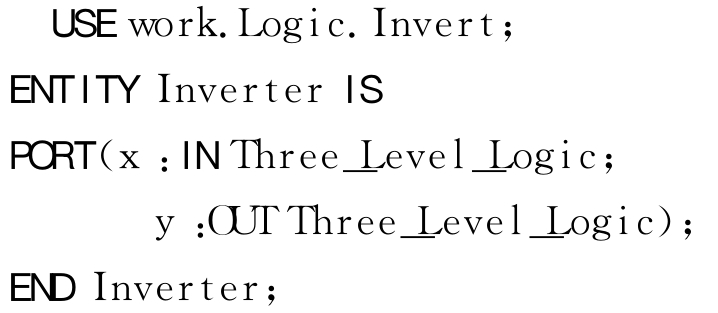

一个程序包所定义的项对另一个单元并不是自动可见的,如果在某个VHDL单元之前加上USE语句,则可以使得程序包说明中的定义项在该单元中可见。如下例:

--假定上述程序包Logic的说明部分已经存在

--下面的USE语句使得Three_level_logic和Invert

--对实体说明成为可见

USE work.Logic.Three_Level_Logic;

--结构体部分继承了实体说明部分的可见性,所以不必再使用USE语句

USE语句后跟保留字ALL,表示使用库/程序包中的所有定义。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。