【摘要】:前面分别介绍了VHDL文本设计方法和原理图设计方法,实际上,很多较复杂的设计采用的是两者的结合。即采用VHDL与原理图混合方式来进行设计。一般情况下,使用VHDL语言描述底层模块,再应用原理图设计方法设计顶层原理图文件。下面以一个十六进制计数器译码显示器的设计来说明设计的流程。保存原理图,并把此原理图设置成当前项目,最后开始编译和仿真。

5.6 VHDL与原理图混合设计方式

前面分别介绍了VHDL文本设计方法和原理图设计方法,实际上,很多较复杂的设计采用的是两者的结合。即采用VHDL与原理图混合方式来进行设计。一般情况下,使用VHDL语言描述底层模块,再应用原理图设计方法设计顶层原理图文件。下面以一个十六进制计数器译码显示器的设计来说明设计的流程。

1)十六进制计数器的VHDL设计

新建一个文本编辑窗口,在窗口中输入例5.3的十六进制计数器的VHDL源程序。

【例5.3】

文件保存通过编译后,选择菜单“File”→“Create Default Symbol”,创建一个图形元件,如图5.69所示。

图5.69 CNT4B元件符号图

2)七端显示译码器的VHDL设计

七端显示译码器的VHDL源程序如例5.4所示。

【例5.4】

![]()

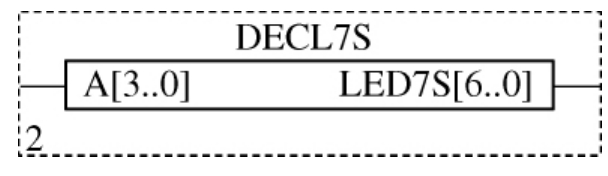

将文件保存放在与例5.3同一目录中,并创建元件符号,如图5.70所示。

图5.70 DECL7S元件符号图

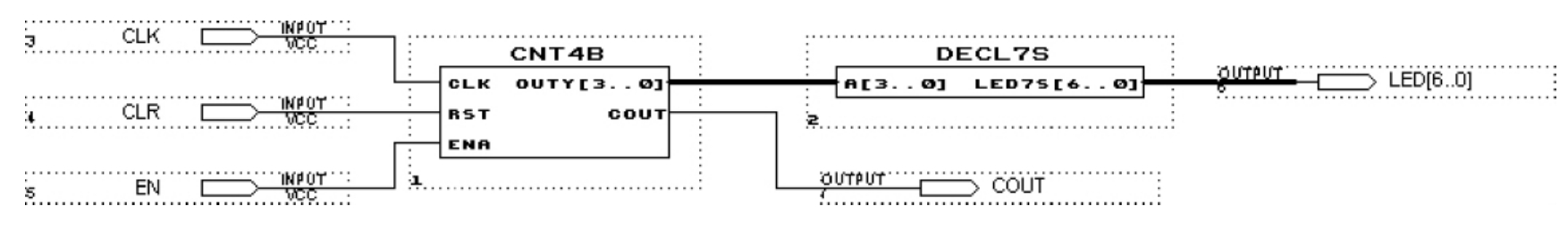

3)顶层原理图设计

在同一目录中新建一个原理图,点击右键,在出现的快捷菜单中选择“Enter Symbol...”,就可以调用前面创建的两个图形元件,绘出如图5.71所示的原理图。保存原理图,并把此原理图设置成当前项目,最后开始编译和仿真。仿真波形如图5.72所示。

图5.71 顶层原理图

图5.72 仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。