【摘要】:在时序电路中,是以时钟信号作为驱动信号的,也就是说时序电路在时钟信号的边沿到来时,状态才会发生改变。时钟作为敏感信号的描述方式有两种:触发器的初始状态应用复位信号来设置,复位信号对触发器复位的操作不同,使其可以分为同步复位和非同步复位两种。在用VHDL描述时,同步复位一定在时钟为敏感信号的进程中定义,且用IF语句来描述必要的复位条件。

6.2.1 时钟信号和复位信号

1)时钟信号描述

在时序电路中,是以时钟信号作为驱动信号的,也就是说时序电路在时钟信号的边沿到来时,状态才会发生改变。因此,在时序电路中,时钟信号是非常重要的,它是时序电路的执行条件。

在用VHDL描述时序逻辑电路时,通常采用时钟进程的形式来描述;也就是说,时序逻辑电路中进程的敏感信号是时钟信号。时钟作为敏感信号的描述方式有两种:

①时钟信号显式地出现在PROCESS语句后面的敏感信号表中。

②时钟信号没有显式地出现在PROCESS语句后面的敏感信号表中,而是出现在WAIT语句的后面。

描述时钟边沿时,一定要指定是上升沿还是下降沿,这一点可以使用时钟信号的属性描述来达到。

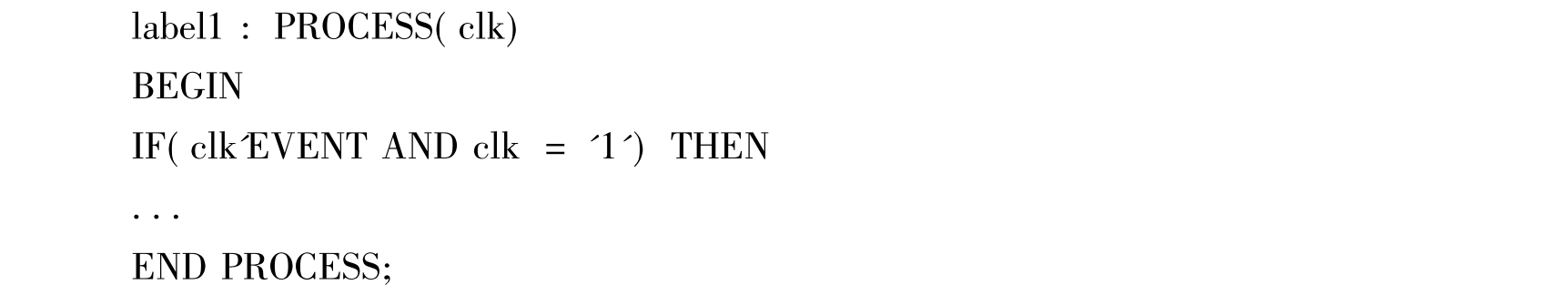

(1)时钟上升沿描述

时钟上升沿是指时钟信号的逻辑值从0跳变到1。

描述1:

描述2:

![]()

(2)时钟下升沿描述

时钟下升沿是指时钟信号的逻辑值从1跳变到0。

描述1:

描述2:

2)触发器的同步和非同步(异步)复位

触发器的初始状态应用复位信号来设置,复位信号对触发器复位的操作不同,使其可以分为同步复位和非同步复位两种。所谓同步复位就是当复位信号有效且给定的时钟边沿到来时,触发器才被复位;而非同步复位则是一旦复位信号有效,触发器就被复位。

(1)同步复位。在用VHDL描述时,同步复位一定在时钟为敏感信号的进程中定义,且用IF语句来描述必要的复位条件。

(2)异步复位。在进程的敏感信号中,除时钟信号以外,还应加上复位信号。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。