实验三 七段数码显示译码器设计

(1)实验目的

学习七段数码显示译码器设计;学习VHDL的多层次设计方法。

(2)实验原理

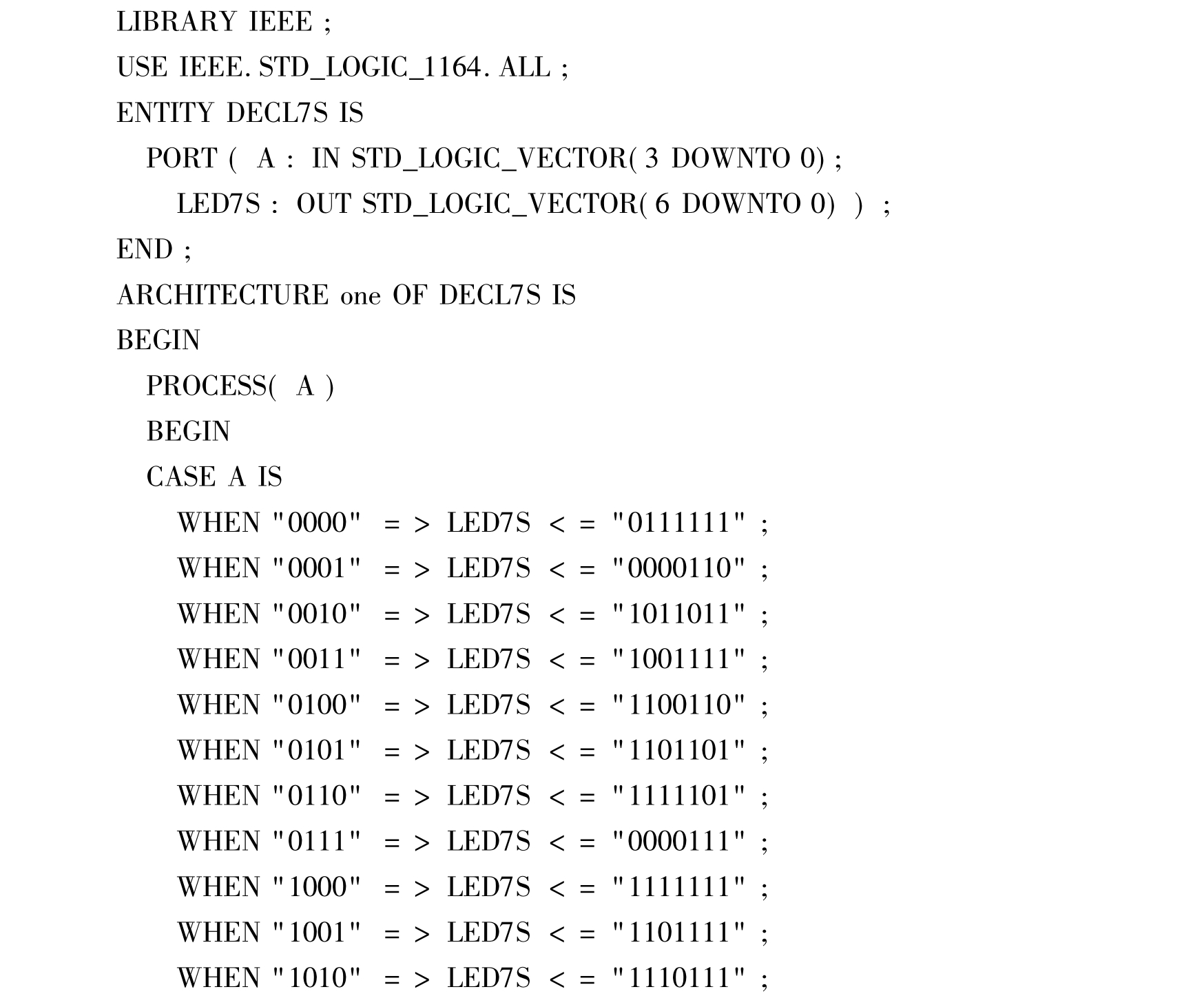

七段数码是纯组合电路,通常小规模专用IC如74或4000系列的器件只能作十进制BCD码译码;然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示需要,最方便的方法就是利用译码程序在FPGA/CPLD中实现。为了简化过程,首先完成七段BCD码译码器的设计。例8.2为7段BCD码译码器,输出信号LED7S的7位分别接如图8.1所示数码管的七个段,高位在左,低位在右。例如当LED7S输出为“1101101”时,数码管的七个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1,接有高电平的段发亮,数码管显示“5”。

图8.1 共阴数码管及其电路

【例8.2】

(3)实验内容1

说明例8.2中各语句的含义以及该例的整体功能。在MAX+plusII上对该例进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

(4)实验内容2

进行引脚锁定及硬件测试。建议选用实验电路模式6,用数码管8显示译码输出(PIO46-PIO40),键8/7/6/5四位控制输入,硬件验证译码器的工作性能。

(5)实验内容3

将例8.2改成十六进制七段译码器重复以上实验。

(6)思考题

讨论语句WHEN OTHERS=>NULL的作用,对于不同的VHDL综合器,此句是否具有相同的含义和功能?

(7)附加实验内容

用例化语句按图8.2的方式,以例8.1和例8.2为底层元件,完成顶层文件设计,并重复以上实验过程。对于引脚锁定和实验,建议选用电路模式6,用数码管8显示译码输出,用键3作为时钟输入(每按两次键为1个时钟脉冲),或直接接时钟信号clock0。

图8.2 计数器和译码器连接电路的顶层文件原理图

(8)实验报告

根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析、硬件测试和实验过程;设计程序、程序分析报告、仿真波形图及其分析报告。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。