【摘要】:完成Cadence设计软件环境设置后,将给定的D触发器电路图通过Cadence Virtuoso Schematic Editor绘制出来,并通过Cadence Virtuoso Layout Editor绘制触发器版图,再通过物理验证。

情境3 触发器版图设计

【学习目标】

(1)熟悉D触发器原理;

(2)能通过Cadence Virtuoso Schematic Editor进行较复杂电路的电路图编辑;

(3)能通过Cadence Virtuoso Layout Editor进行较复杂电路的版图编辑;

(4)能对较复杂电路进行DRC和LVS。

【重点难点】

(1)根据电路进行简单的版图布局;(2)D触发器的版图绘制;

(3)缩小版图的技巧。

【参考学时】

参考学时为6学时。

1.任务目的

通过设计D触发器版图,掌握Cadence软件环境设置、设计规则,Cadence Virtuoso Schematic Editor和Cadence Virtuoso Layout Editor操作,以及物理验证流程。

2.任务要求

完成Cadence设计软件环境设置后,将给定的D触发器电路图通过Cadence Virtuoso Schematic Editor绘制出来,并通过Cadence Virtuoso Layout Editor绘制触发器版图,再通过物理验证。

3.电路图

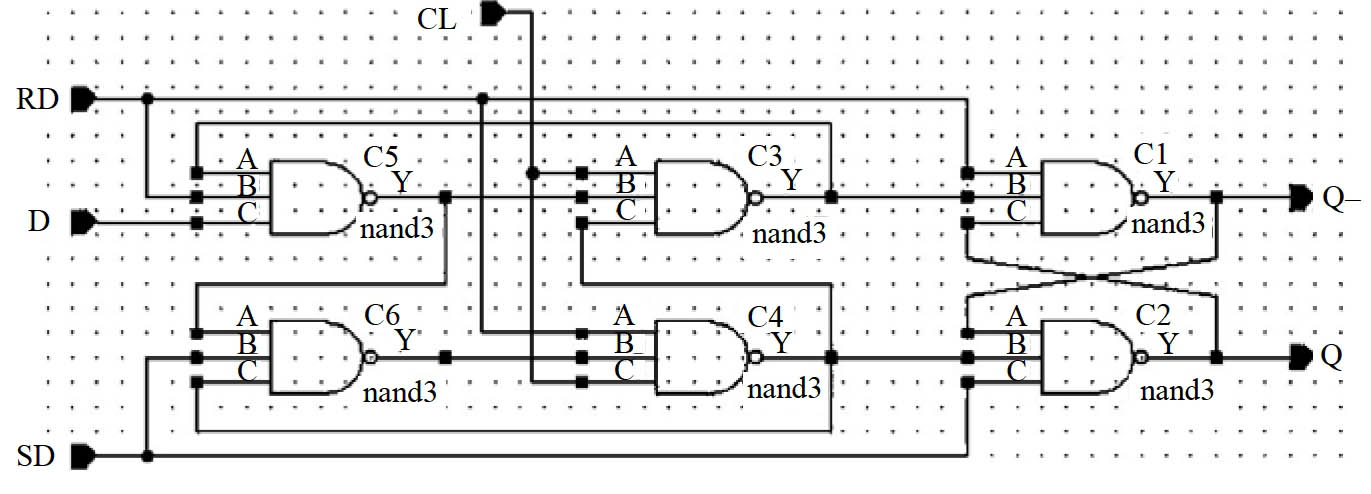

D触发器电路图如图3.1所示。

图3.1 触发器电路图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。