3.2 VHDL程序的编译与仿真

Active-HDL软件工具的基本操作顺序如下:

创建新的设计(Create New Design)

编写VHDL程序

编译VHDL程序

仿真验证VHDL程序

下面以第二章的二选一选择器为例,介绍VHDL程序的编写、编译和仿真。

1.创建新的设计(Create New Design)

打开Active-HDL

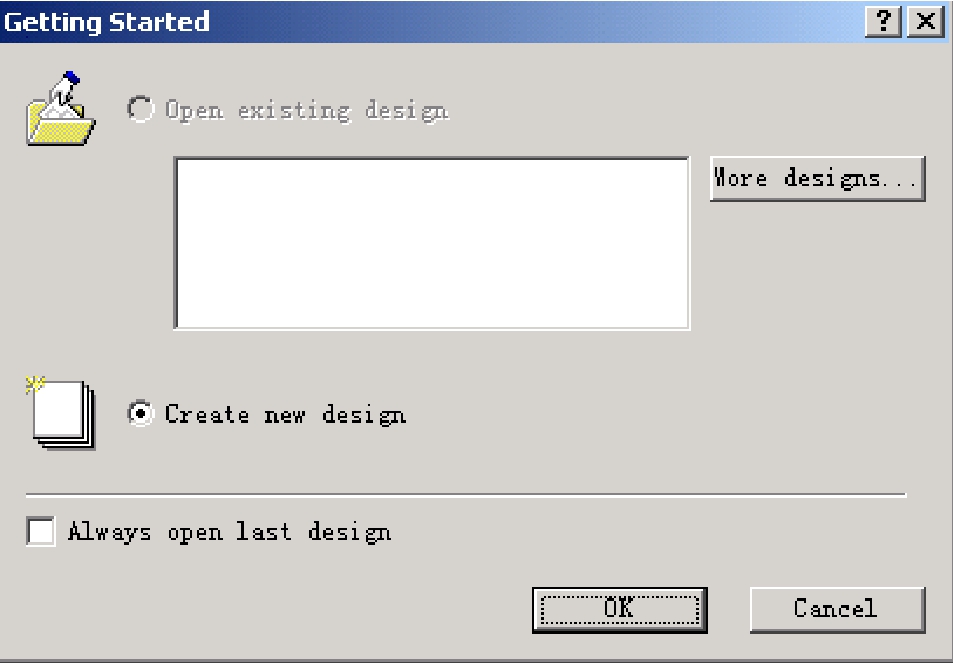

如果用户是安装好Active-HDL后第一次使用,运行软件后首先进入如图3.2所示的界面。

图3.2 运行Active-HDL软件后的初始界面

创建新的设计

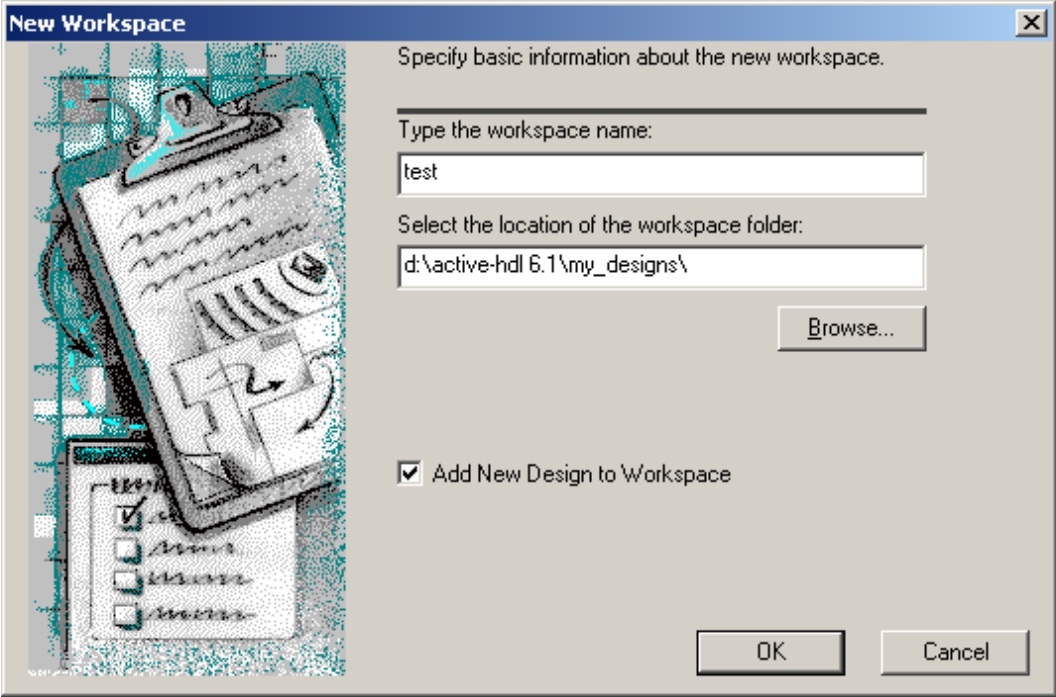

在图3.2中选择“Create New Design”项,点击“OK”,即进入如图3.3所示的界面,在输入窗中可定义workspace名,比如命名为“test”。

图3.3 定义workspace名

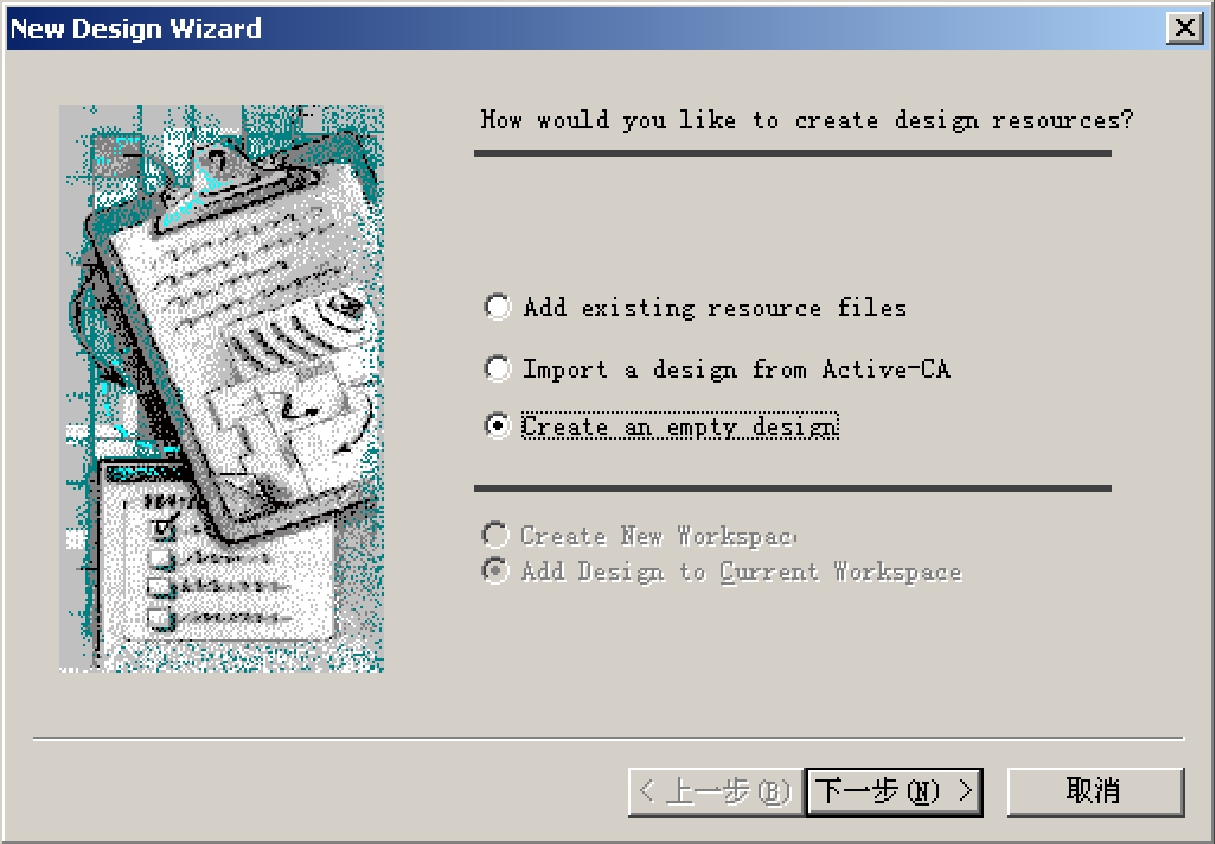

点击“OK”后,即进入新设计向导页面(如图3.4所示)。

图3.4 新设计向导首页面

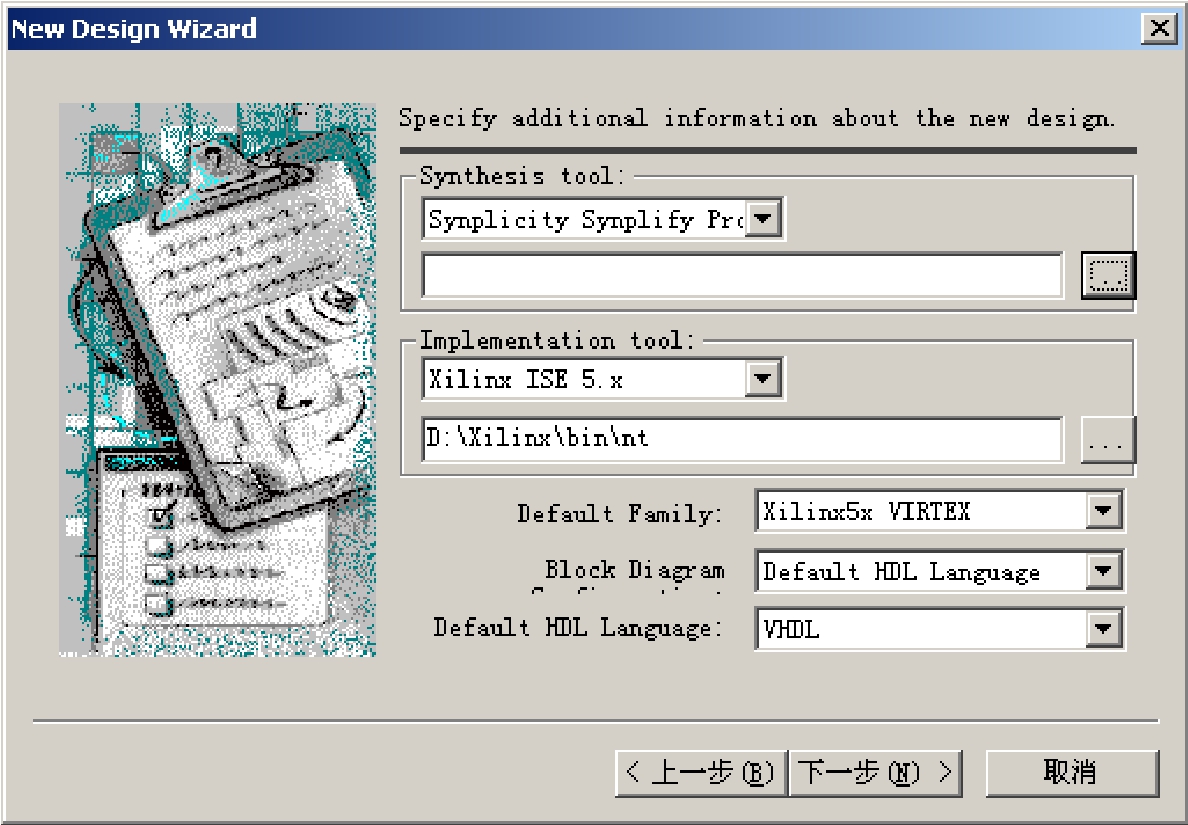

选择“Create an empty design”,点击“下一步”,即进入新设计的设置(如图3.5所示)。

图3.5 新设计的设置

在新设计设置页面中可选择设置综合工具和后端物理实现工具,如果暂时不关心后期设计工具的选择,可直接点击下一步,进入新设计命名页面(如图3.6所示)。

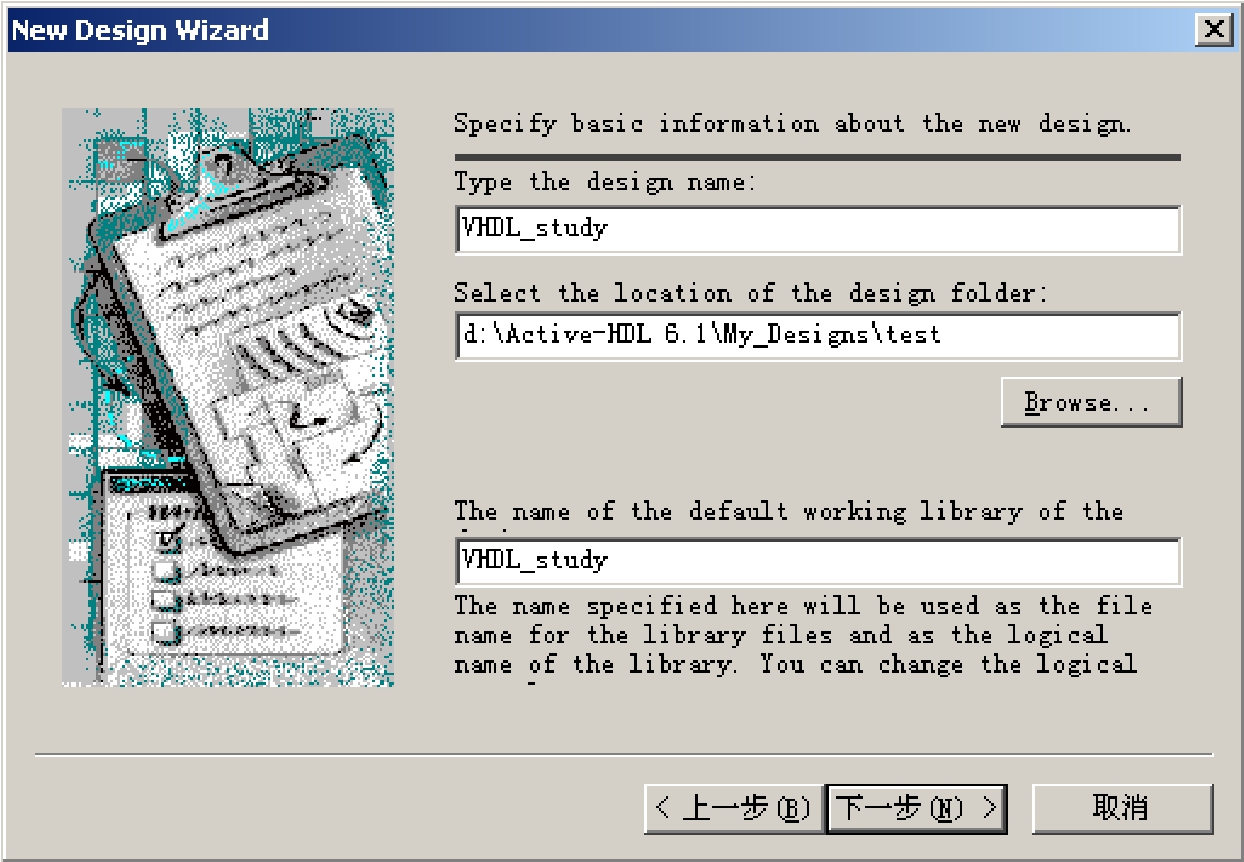

在图3.6中为新设计命名,比如命名为“VHDL_study”,然后点击下一步,即完成新设计的创建。接下来就可以开始VHDL程序的编写了。

图3.6 新设计的命名

2.编写VHDL程序

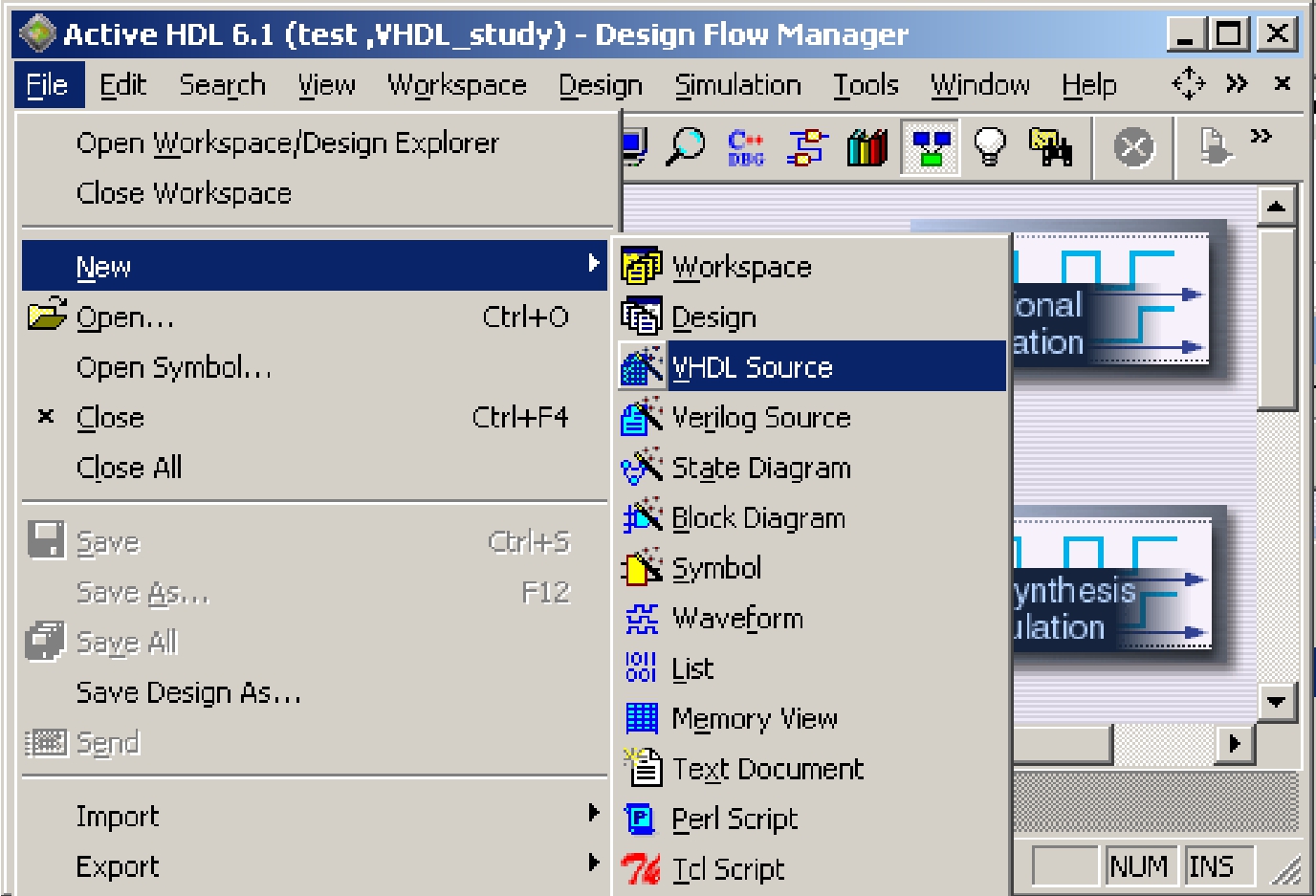

编写VHDL程序,首先需要新建一个VHDL文件,如图3.7所示,通过选择“File→New→VHDL Source”即可新建VHDL文件。

图3.7 新建VHDL源文件

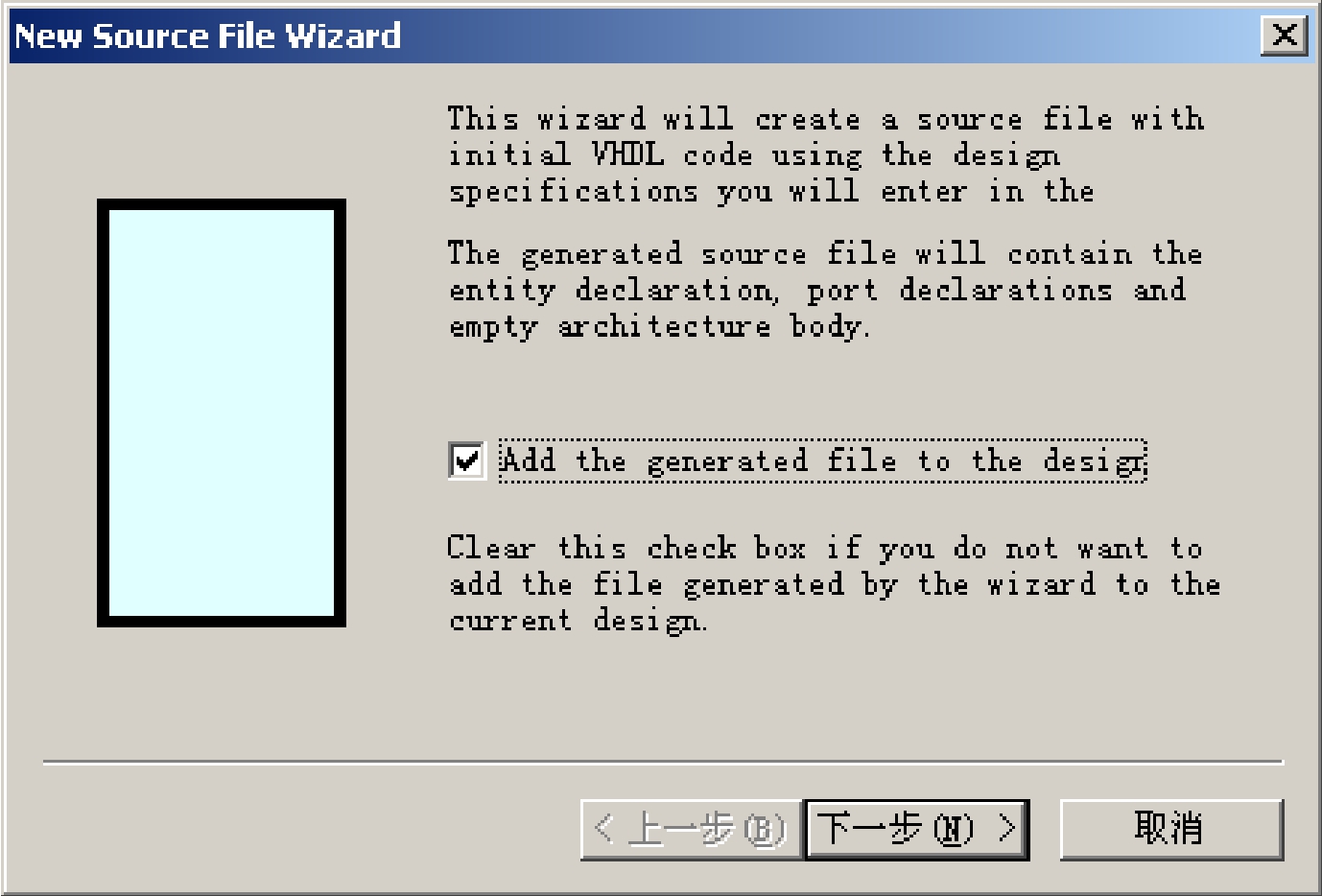

上一步操作将进入如图3.8所示的源文件新建向导对话框。

图3.8 源文件新建向导

点击“下一步”进入如图3.9所示的新建VHDL源文件命名对话框,在图3.9中除了可以为VHDL源文件命名外,还可以分别为VHDL程序的实体和构造体命名。

图3.9 新建VHDL源文件的命名

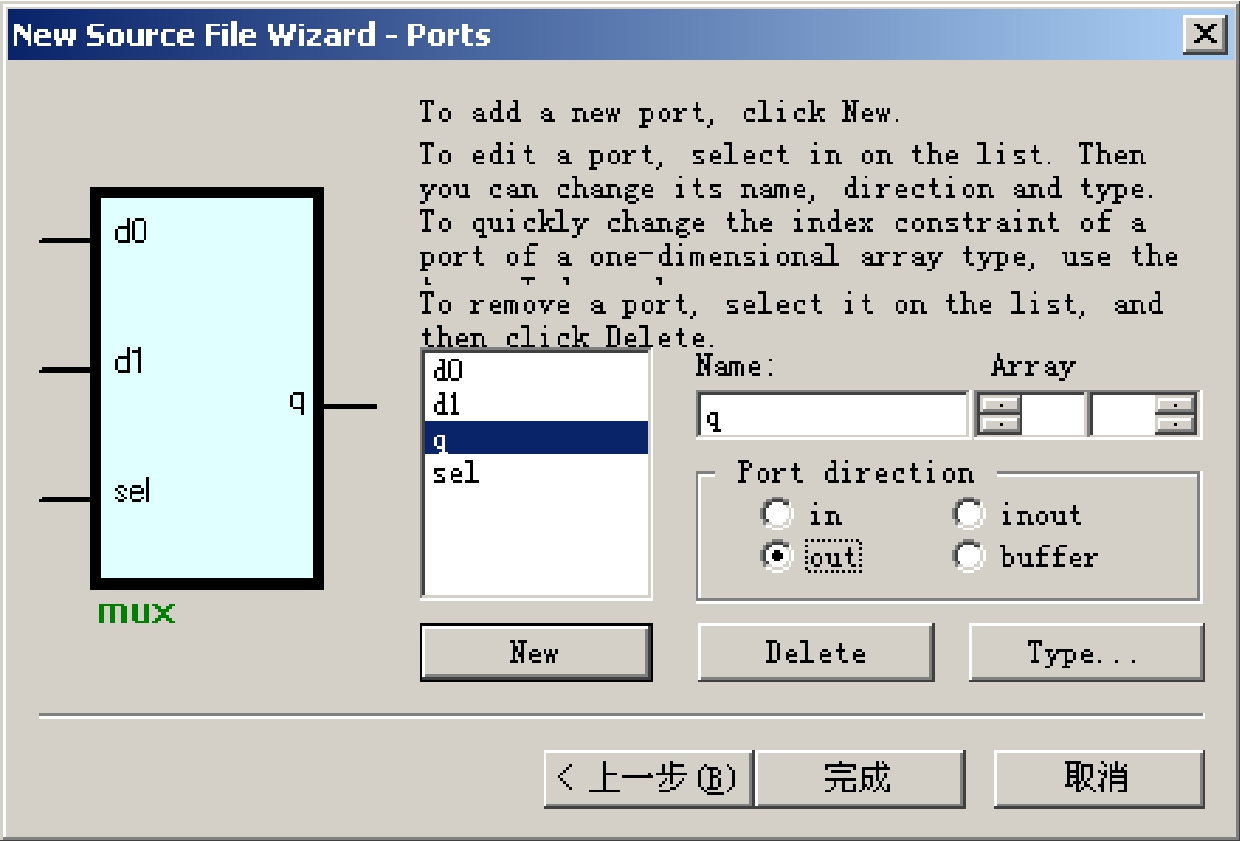

点击“下一步”进入如图3.10所示的VHDL程序端口设置窗口。已知第二章的二选一选择器共有三个输入端口d0、d1、sel和一个输出端口q。

如图3.10所示,可以依次设置这四个端口的端口名和端口方向,其中要注意端口方向(Port direction)选项的正确选择,输入端口选择“in”,输出端口选择“out”。

图3.10 VHDL程序的端口设置

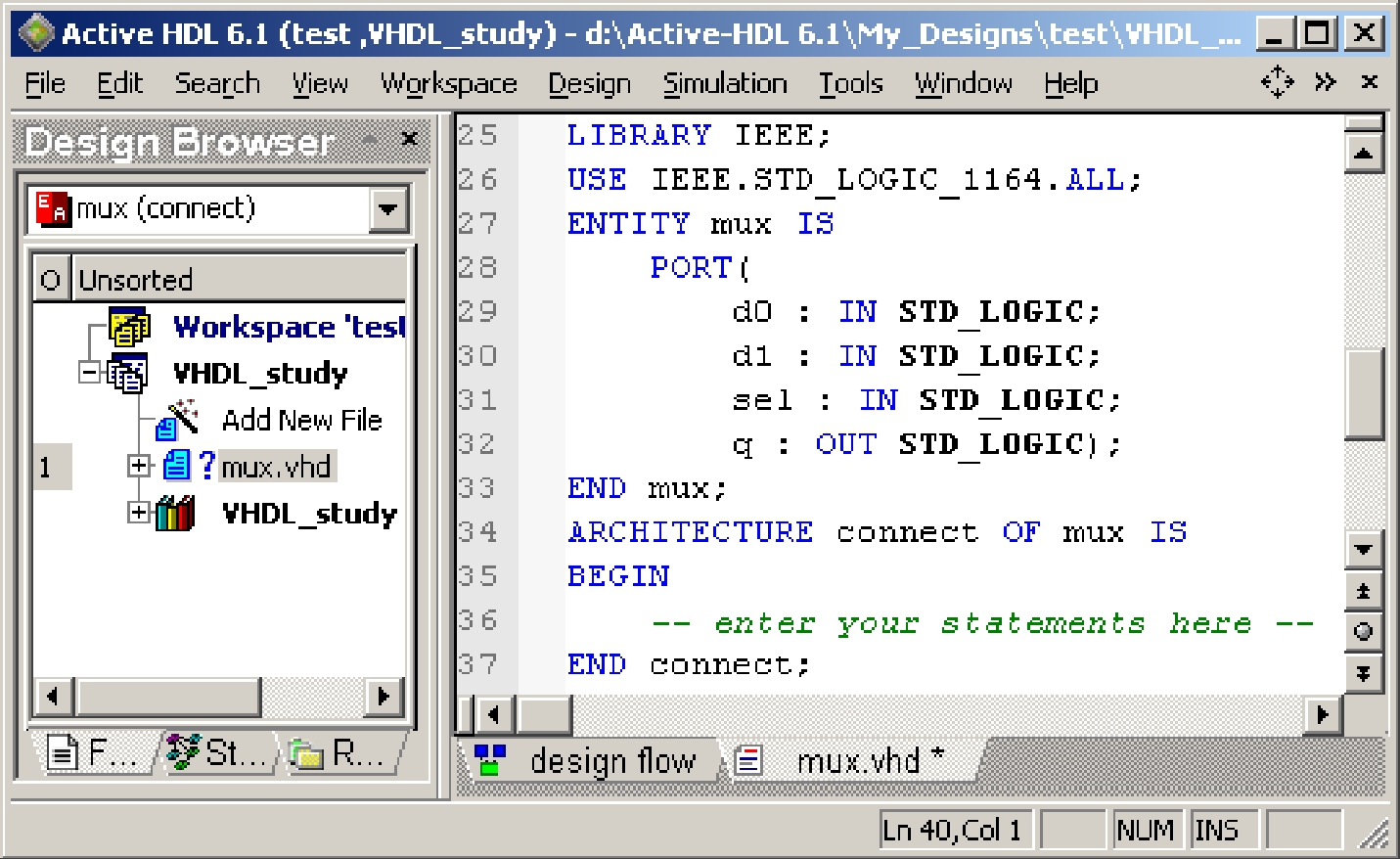

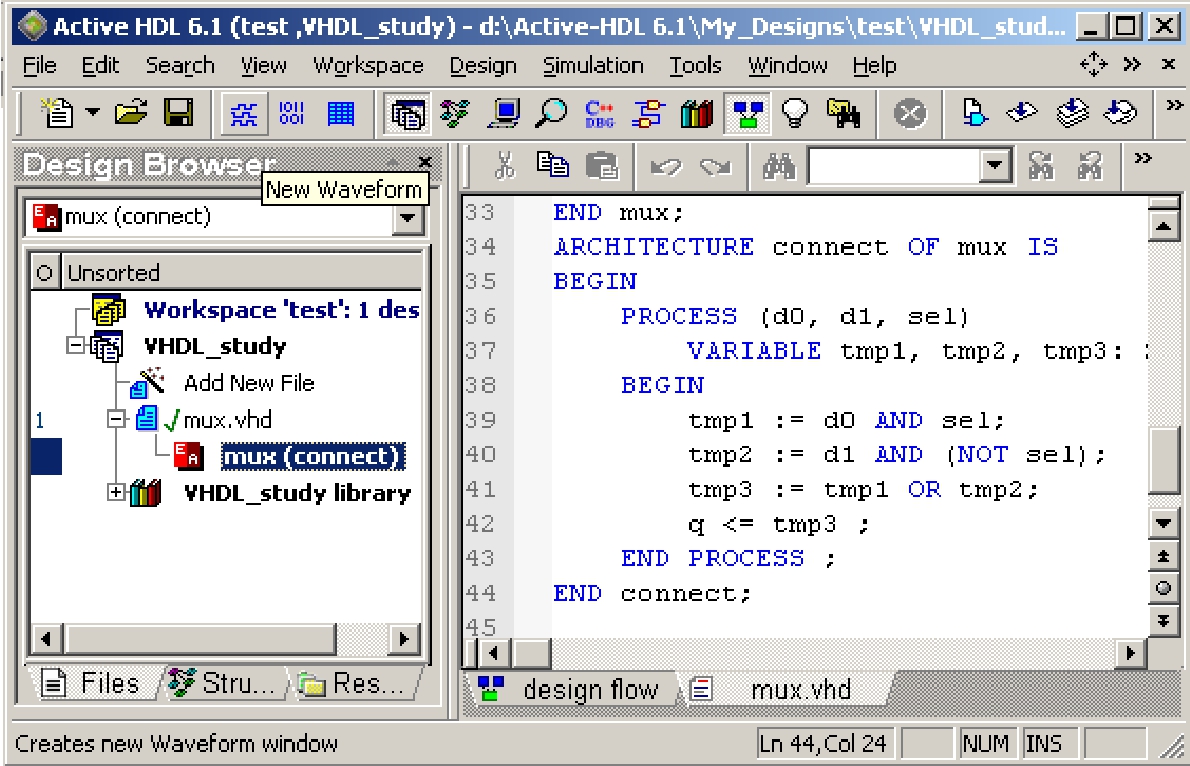

点击“完成”进入后,即可自动生成VHDL源文件的部分代码,如图3.11所示。从图3.11可以发现,实体部分已经生成,构造体的框架也已经自动生成。现在我们只需要将二选一选择器的构造体内的功能描述语句录入即可完成VHDL程序的编写,最后别忘了Save源文件,Save功能的快捷按键为“Ctrl+S”。

图3.11 VHDL源文件新建向导自动生成的源代码部分

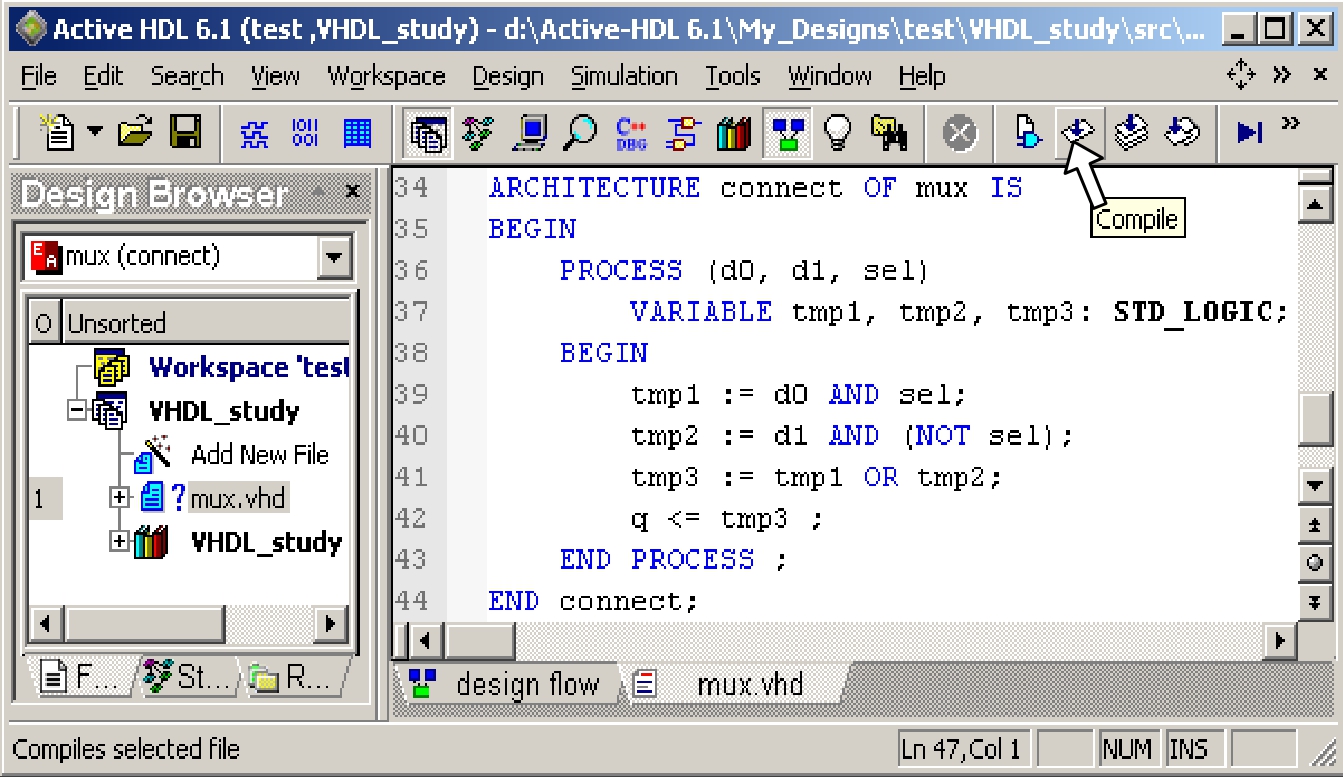

3.编译VHDL程序

完成VHDL程序的编写后,就该进行编译操作了。编译可以检查出源程序的语法错误。编译操作可参见图3.12中点击箭头所示的快捷按钮进行;或者点击主界面菜单栏上的“Design”,通过选择“Design→Compile”启动编译操作;还可以通过快捷按键“F11”来启动编译操作。在未编译之前,Design Browser窗口中二选一选择器的VHDL程序文件名mux.vhd前面会以蓝色小问号“?”标志。

图3.12 VHDL程序的编译

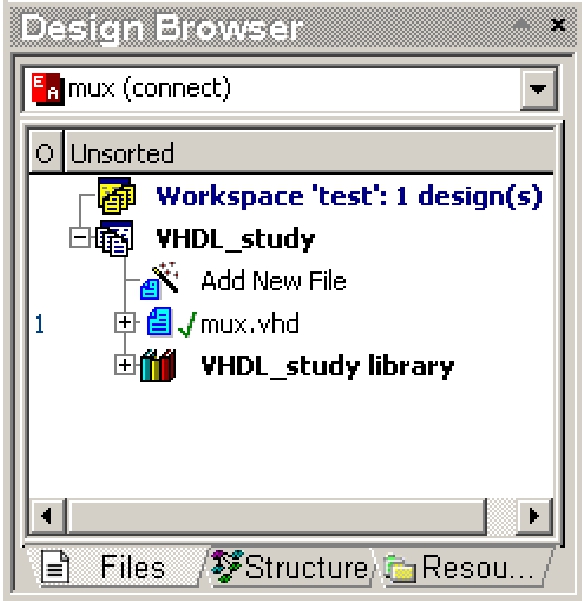

如果编译成功、没有错误,则Design Browser窗口中二选一选择器的VHDL程序文件名mux.vhd前面会标上绿色小勾“√”,如图3.13所示。如果源程序中有错误,则编译后VHDL程序文件名mux.vhd前面会标上红色小叉“×”,同时在源程序中有错误的代码行也会以红色波浪线标出。用鼠标指向错误行,Active-HDL会自动提示出错的类型。反复修改直到没有错误,编译成功为止。

图3.13 VHDL程序编译正确后的结果

4.仿真验证VHDL程序

编译成功后,即可对VHDL程序进行仿真了。

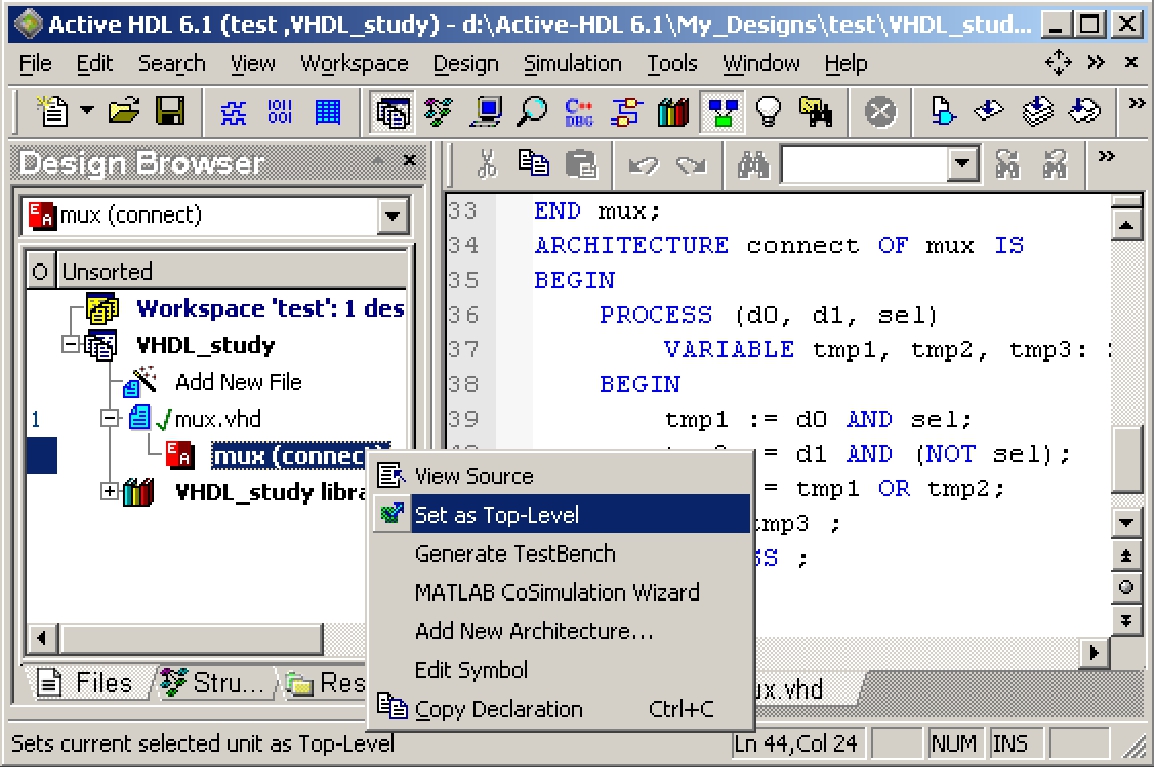

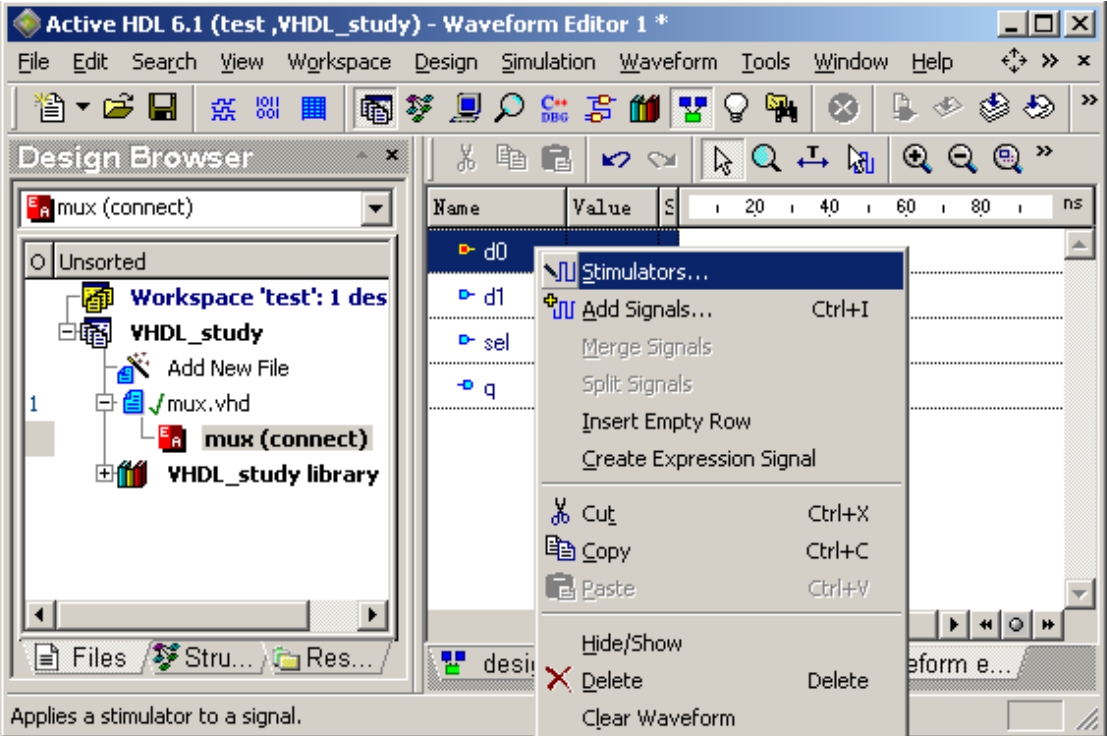

在VHDL源文件编译完成后,单击图3.14中“Design Browser”窗口中编译通过的文件mux.vhd前的小加号“+”,出现一个子项,这就是源文件中的实体和构造体,如图3.14所示,选中它,单击鼠标右键,在弹出菜单中选择“Set as Top-level”,即完成仿真对象的设定。接下来如图3.15中箭头所示,点击“New Waveform”快捷按钮,即可打开仿真波形观测窗。如图3.16所示,通过选择“Waveform→Add signals”启动信号添加对话框。

图3.14 设定仿真对象

图3.15 启动仿真波形观测窗

图3.16 启动信号添加对话框

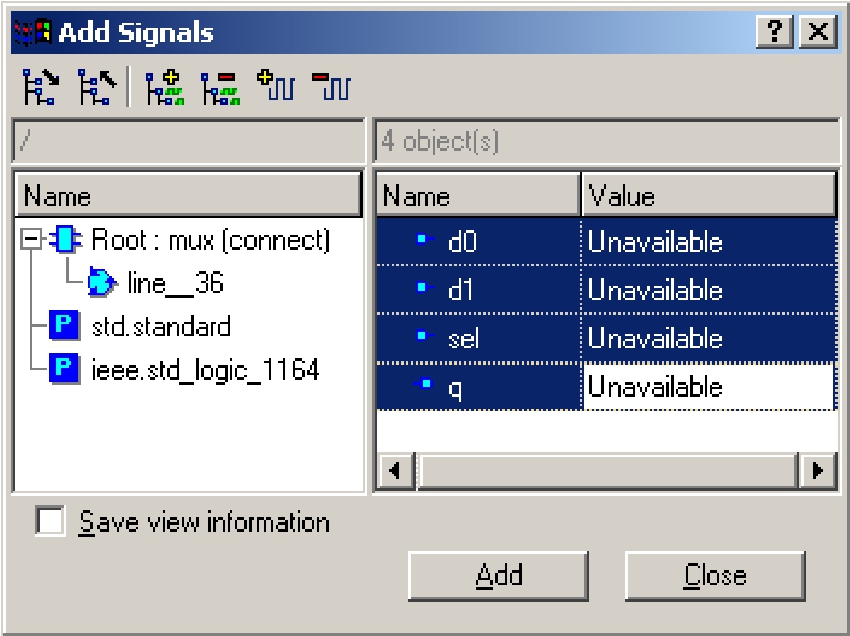

图3.17 信号添加对话框

如图3.17所示,选中欲加入波形观测窗的信号,点击“Add”,这些信号就被添加到了如图3.18所示的窗口中。接下来就是为二选一选择器的输入信号添加激励了,如图3.18所示,选中信号,单击鼠标右键,在弹出菜单中选择“Stimulators”启动测试激励添加功能。

图3.18 启动测试激励添加功能

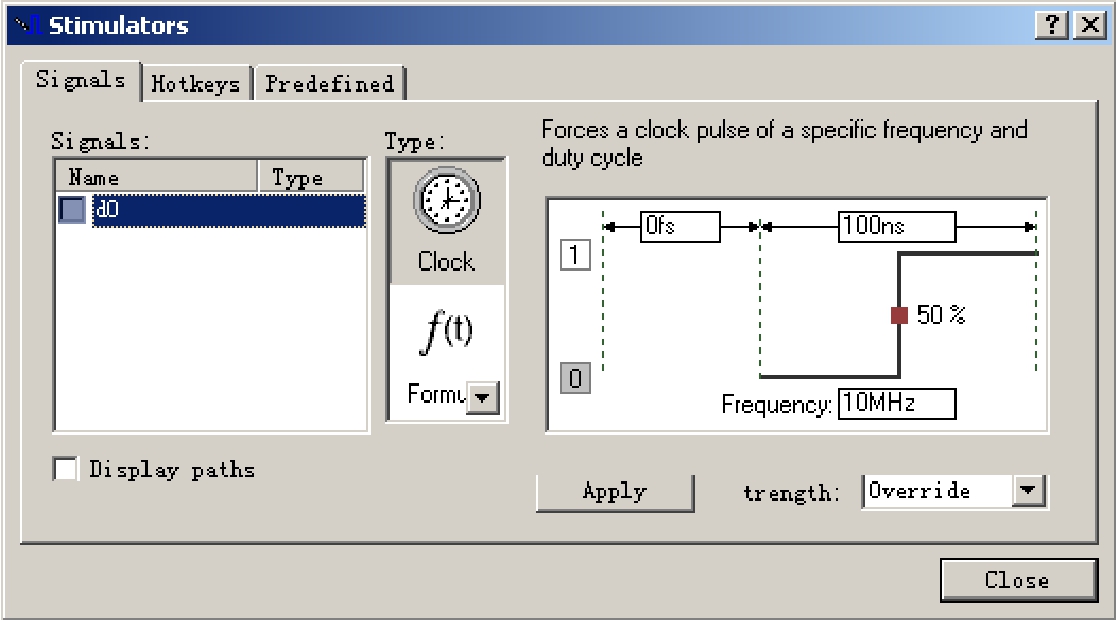

图3.19 Clock类型激励的添加

如图3.19所示,为输入信号d0添加Clock类型的激励,设置为10MHz信号,点击“Apply”按钮完成激励的添加。用同样的方法可以为输入信号d1添加20MHz 的Clock类型激励。

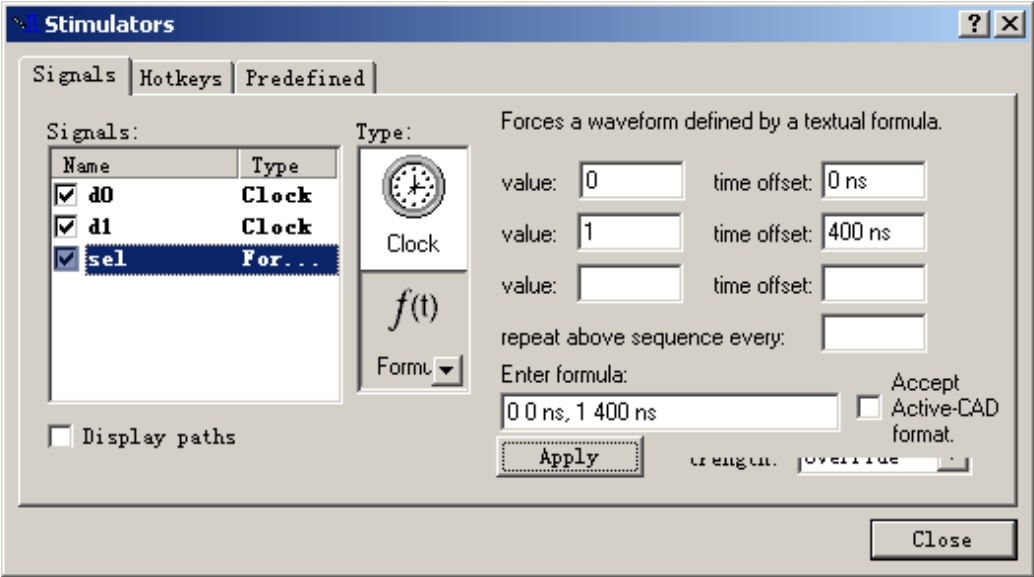

如图3.20所示,为二选一选择器的选择使能输入信号sel添加Formula类型的激励,设定0ns时sel信号值为“0”,直到400ns时sel信号值变为“1”,然后保持。

图3.20 Formula类型激励的添加

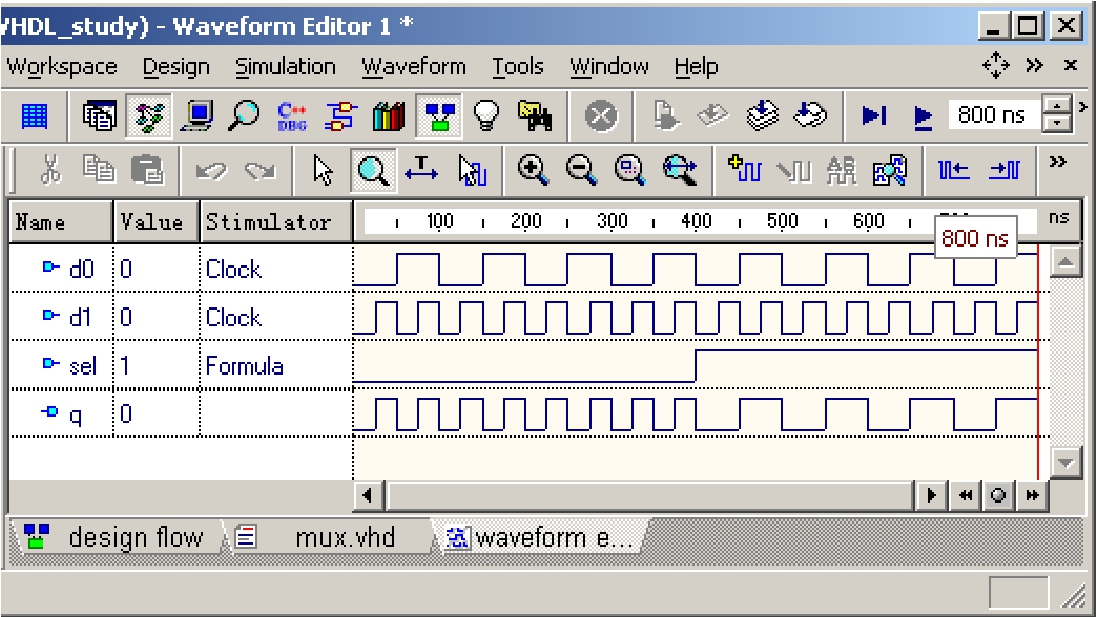

完成激励添加后,点击“ ”按钮,即可运行仿真,得到仿真波形如图3.21所示。通过读波形可以发现,该二选一选择器的逻辑功能完全正确。

”按钮,即可运行仿真,得到仿真波形如图3.21所示。通过读波形可以发现,该二选一选择器的逻辑功能完全正确。

到此为止,仿真顺利完成。

图3.21 仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。