实验十四 触发器及其应用

一、实验目的

1.掌握基本RS、JK、T和D触发器的逻辑功能。

2.掌握集成触发器的功能和使用方法。

3.熟悉触发器之间相互转换的方法。

二、实验原理

触发器是能够存储1位二进制码的逻辑电路,它有两个互补输出端,其输出状态不仅与输入有关,而且还与原先的输出状态有关。触发器有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存储器件,是构成各种时序电路的最基本逻辑单元。

1.基本RS触发器

图6-54为由两个与非门交叉耦合构成的基本RS触发器,它是无时钟控制低电平直接触发的触发器。基本RS触发器具有置“0”、置“1”和保持三种功能。通常称 为置“1”端,因为

为置“1”端,因为 =0时触发器被置

=0时触发器被置 时触发器被置

时触发器被置 时状态保持,当

时状态保持,当 时为不定状态,应当避免这种状态。

时为不定状态,应当避免这种状态。

基本RS触发器也可以用两个“或非门”组成,此时为高电平有效。

图6-54 二与非门组成的基本RS触发器

基本RS触发器的逻辑符号见图6-54(b),二输入端的边框外侧都画有小圆圈,这是因为置1与置0都是低电平有效。

2.JK触发器

图6-55 JK触发器的引脚逻辑图

在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。引脚逻辑图如图6-55所示;JK触发器的状态方程为:

其中,J和K是数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组成“与”的关系。 为两个互补输入端。通常把

为两个互补输入端。通常把 的状态定为触发器“0”状态;而把Q=1,

的状态定为触发器“0”状态;而把Q=1, 定为“1”状态。

定为“1”状态。

JK触发器常被用作缓冲存储器,移位寄存器和计数器。

CC4027是CMOS双JK触发器,其功能与74LS112相同,但采用上升沿触发,R、S端为高电平有效。

3.T触发器

在JK触发器的状态方程中,令J=K=T则变换为:

这就是T触发器的特性方程。由上式有:

当T=1时

当T=0时

即当T=1时,为翻转状态;当T=0时,为保持状态。

4.D触发器

在输入信号为单端的情况下,D触发器用起来更为方便,其状态方程为:

Qn+1=D

其输出状态的更新发生在CP脉冲的上升沿,故又称为上升沿触发的边沿触发器,触发器的状态只取决于时钟到来前D端的状态,D触发器的应用很广,可用作数字信号的寄存,移位寄存,分频和波形发生等。有很多型号可供各种用途的需要而选用。如双D(74LS74,CC4013),四D(74LS175,CC4042),六D(74LS174,CC14174),八D(74LS374)等。

图6-56为双D(74LS74)的引脚排列图。

5.触发器之间的相互转换

在集成触发器的产品中,每一种触发器都有自己固定的逻辑功能。但是可以利用转换的方法获得具有其他功能的触发器。例如将JK触发器的J、K两端接在一起,并认它为T端,就得到所需的T触发器。

JK触发器也可以转换成为D触发器,如图6-57所示。

图6-56 双D触发器的引脚排列图

图6-57 JK触发器转换成为D触发器

三、实验设备与器材

1.数字逻辑电路实验箱。

2.双踪示波器,数字万用表。

3.芯片74LS00、74LS04、74LS10、74LS74(或CC4013)、74LS112(或CC4027)、74LS02。

四、实验内容及实验步骤

1.测试基本RS触发器的逻辑功能

按图6-54,用两个与非门组成基本RS触发器,输入端 接逻辑电平输出插孔(拨位开关输出端),输出端

接逻辑电平输出插孔(拨位开关输出端),输出端 接逻辑电平显示输入插孔(发光二极管输入端),测试它的逻辑功能并画出真值表将实验结果填入表内。

接逻辑电平显示输入插孔(发光二极管输入端),测试它的逻辑功能并画出真值表将实验结果填入表内。

将两个与非门换成两个或非门,要求同上,测试它的逻辑功能并画出真值表将实验结果填入表内。

2.测试JK触发器74LS112的逻辑功能

(1)测试JK触发器的复位、置位功能

任取一个JK触发器 端接逻辑电平输出插孔,CP接单次脉冲源,输出端Q

端接逻辑电平输出插孔,CP接单次脉冲源,输出端Q 接逻辑电平显示输入插孔。要求改变

接逻辑电平显示输入插孔。要求改变 和CP处于任意状态),并在

和CP处于任意状态),并在 =1)或

=1)或 )作用期间任意改变J、K和CP的状态,观察

)作用期间任意改变J、K和CP的状态,观察 的状态,自拟表格并记录之。

的状态,自拟表格并记录之。

(2)测试JK触发器的逻辑功能

不断改变J、K和CP的状态,观察 的状态变化,观察触发器状态更新是否发生在CP的下降沿,记录之。

的状态变化,观察触发器状态更新是否发生在CP的下降沿,记录之。

(3)将JK触发器的J、K端连在一起,构成T触发器

在CP端输入1Hz连续脉冲,观察Q端的变化,用双踪示波器观察CP、Q和 的波形,注意相位关系,描绘之。

的波形,注意相位关系,描绘之。

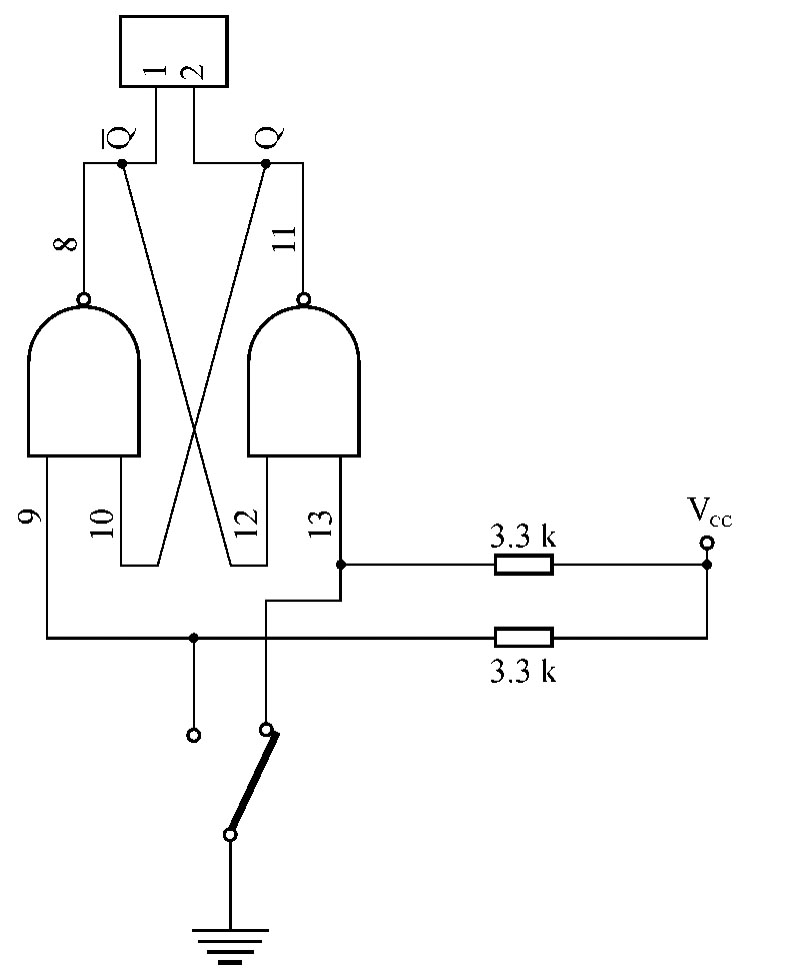

图6-58 去抖动电路图

(4)JK触发器转换成D触发器

按图6-57连线,方法与步骤同上,测试D触发器的逻辑功能并画出真值表将实验结果填入表内。

3.RS基本触发器的应用举例

图6-58是由基本RS触发器构成的去抖动电路开关,它是利用基本RS触发器的记忆作用来消除开关震动带来的影响。参考有关资料分析其工作原理,自己在实验电路板上搭建电路来验证该去抖动电路的功能。

4.测试双D触发器74LS74的逻辑功能

(1)测试D触发器的复位、置位功能

测试方法与步骤同实验内容2(1),只是它们的功能引脚不同,相关的管脚分布参见附录,自拟表格记录。

(2)测试D触发器的逻辑功能

按表6-19要求进行测试,并观察触发器状态是否发生在CP脉冲的上升沿(即由0变1),记录之。

表6-19 测试D触发器的逻辑功能

五、实验预习要求

1.复习有关触发器内容,熟悉有关器件的管脚分配。

2.列出各触发器功能测试表格。

3.参考有关资料查看74LS112和74LS74的逻辑功能。

六、实验报告要求

1.列表整理各类触发器的逻辑功能。

2.总结观察到的波形,说明触发器的触发方式。

3.利用普通的机械开关组成的数据开关所产生的信号是否可以作为触发器的时钟脉冲信号,为什么?是否可以作为触发器的其他输入端的信号,又是为什么?

4.思考:为什么图6-58所示的去抖动电路能去抖动?

七、触发器的使用规则

1.通常根据数字系统的时序配合关系正确选用触发器,除特殊功能外,一般在同一系统中选择相同触发方式的同类型触发器较好。

2.工作速度要求较高的情况下采用边沿触发方式的触发器较好。但速度越高,越易受外界干扰。上升沿触发还是下降沿触发,原则上没有优劣之分。如果是TTL电路的触发器,因为输出为“0”时的驱动能力远强于输出为“1”时的驱动能力,尤其是当集电极开路输出时上升沿更差,为此选用下降沿触发更好些。

3.触发器在使用前必须经过全面测试才能保证可靠性。使用时必须注意置“1”和置“0”脉冲的最小宽度及恢复时间。

4.触发器翻转时的动态功耗远大于静态功耗,为此系统设计者应尽可能避免同一封装内的触发器同时翻转(尤其是甚高速电路)。

5.CMOS集成触发器与TTL集成触发器在逻辑功能、触发方式上基本相同。使用时不宜将这两种器件同时使用。因CMOS内部电路结构以及对触发时钟脉冲的要求与TTL存在较大的差别。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。