实验三十 组合逻辑电路实验

一、实验目的

1.掌握组合逻辑电路的设计方法。

2.掌握组合逻辑电路的静态测试方法。加深CPLD设计过程的理解,并比较原理图输入和文本输入的优劣。

3.进一步熟悉EDA软件使用的方法和有关可编程逻辑器件方面的知识。

4.学习有关硬件描述语言方面的知识。

二、实验的硬件要求

1.数字逻辑电路实验箱。

2.数字逻辑电路实验箱1032E适配板和7128适配板。

3.PC机。

三、实验内容

1.设计一个四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5时,判别电路输出为1,反之为0。

2.设计四个开关控制一盏灯的逻辑电路,要求合任一开关,灯亮;断任一开关,灯灭。

3.设计一个优先权排队电路,排队顺序为:

A=1 最高优先级

B=1 次高优先级

C=1 最低优先级

要求输出端最高只能有一端为“1”,即只能是优先级较高的输入端所对应的输出端为“1”。

四、实验原理图及相应硬件描述语言

1.四舍五入判别电路原理图(图6-168):

图6-168 四舍五入判别电路原理图

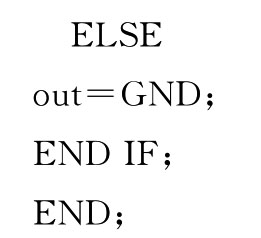

2.四舍五入判别电路AHDL硬件描述语言输入:

3.开关控制电路原理图(见图6-169)

图6-169 开关控制电路原理图

4.开关控制电路AHDL硬件描述语言输入

5.优先权排队电路原理图(见图6-170)

图6-170 优先权排队电路原理图

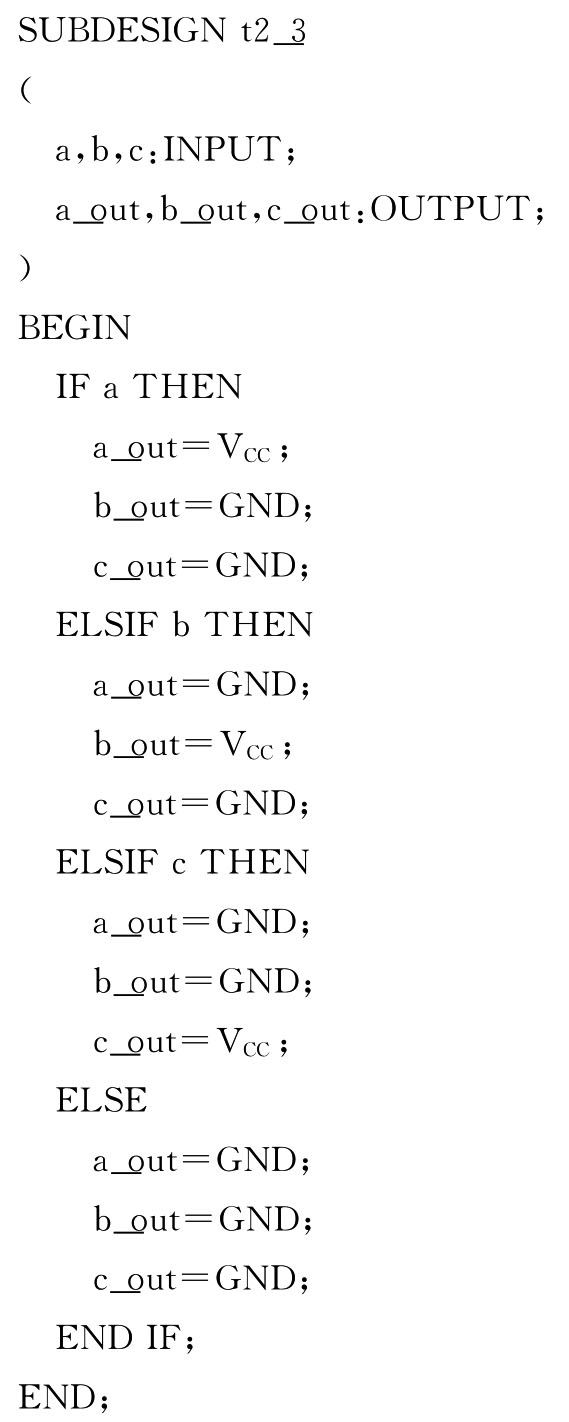

6.优先权排队电路AHDL硬件描述语言输入

说明:以上三种组合逻辑电路的原理图均是用Max+plus II软件完成的,相应的isp-DesignEXPERT软件设计请同学们自己参照实验二十八中该软件的使用方法来完成。

五、实验步骤

1.参照实验指导书中提供的原理图,自己建立新的工程名和文件名,完成上述三种组合逻辑电路的原理图输入和硬件描述语言输入,并编译、下载。

2.利用实验箱中提供的硬件资源来实现上述三种组合逻辑电路的功能。

3.将你熟悉的比较简单的组合逻辑电路用原理图或者语言输入,实现其逻辑功能。

六、实验预习要求

1.仔细阅读本实验指导书的实验二十八,进一步熟悉EDA软件的使用方法。

2.参照本实验的三种组合逻辑电路,熟悉其逻辑功能。

3.自己学习有关硬件描述语言方面的书籍,试着编写一些小程序。

七、实验报告要求

1.将上述三种组合逻辑电路的逻辑功能用表格来表示,并填写表格。

2.自己编写一些用硬件描述语言(VHDL,AHDL等)实现的小程序。

3.写一些对于两种硬件设计输入法的优劣心得。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。