6.1 存储器控制器

6.1.1 存储控制器的特点

S3C2410处理器的存储控制器可以为片外存储器访问提供必要的控制信号,它主要包括以下特点:

(1)支持大、小端模式(通过软件选择).

(2)地址空间:包含8个地址空间,每个地址空间的大小为128M字节,总共有1G字节的地址空间.

(3)除Bank0以外的所有地址空间都可以通过编程设置为8位、16位或32位访问.Bank0可以设置为16位、32位访问.

(4)8个地址空间中,6个地址空间可以用于ROM、SRAM等存储器,2个用于ROM、SRAM、SDRAM等存储器.

(5)7个地址空间的起始地址及空间大小是固定的.

(6)1个地址空间的起始地址和空间大小是可变的.

(7)所有存储器空间的访问周期都可以通过编程配置.

(8)提供外部扩展总线的等待周期.

(9)SDRAM支持自动刷新和掉电模式.

图6-1 S3C2410复位后的存储器地址分配

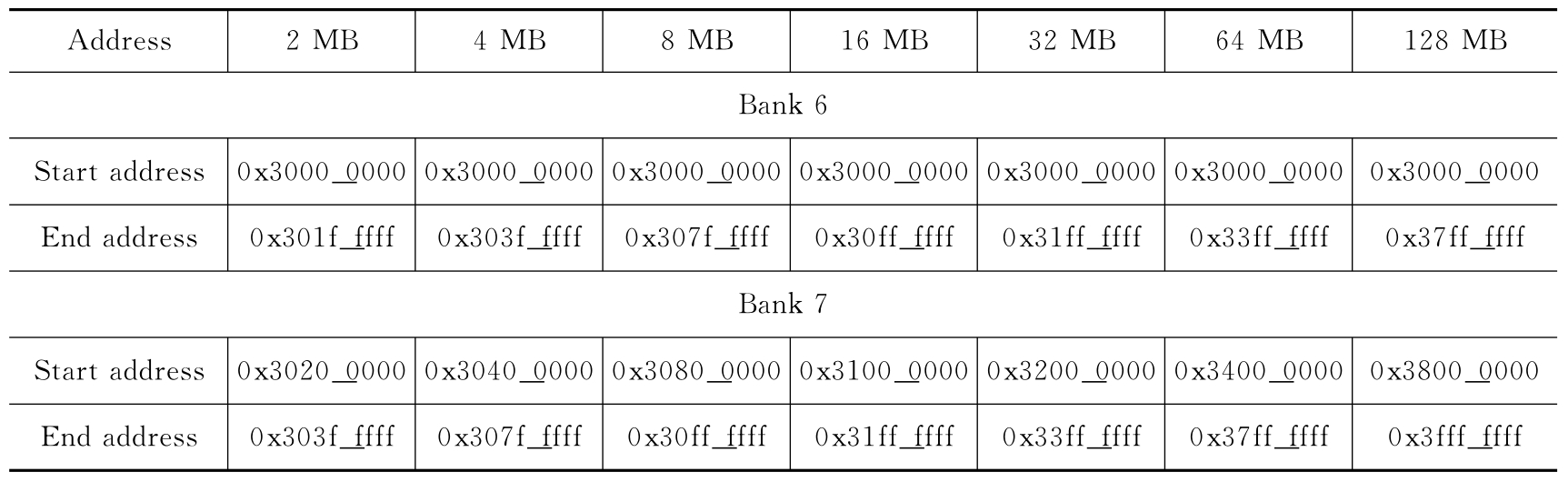

表6-1 Bank6/Bank7地址

注意:Bank6和Bank7的内存大小必须一致.

图6-1为S3C2410复位后的存储器地址分配图.从图中可以看出,特殊功能寄存器位于0x48000000到0x60000000的空间内.Bank0~Bank5的起始地址和空间大小都是固定的,Bank6的起始地址是固定的,但是空间大小和Bank7一样是可变的,可以配置为2M/4M/8M/16M/32M/64M/128M.Bank6和Bank7的详细地址和空间大小的关系可以参考表6-1.

6.1.2 Bank0总线宽度

Bank0(nGCS0)的数据总线宽度可以配置为16位或32位.因为BANK0为启动ROM(映射地址为0x00000000)所在的空间,所以必须在第一次访问ROM前设置BANK0数据宽度,该数据宽度是由复位后OM[1∶0]的逻辑电平决定的,如表6-2所示.

表6-2 数据宽度选择

6.1.3 SDRAM空间地址引脚连接及空间地址配置

SDRAM空间地址引脚连接如表6-3所示,SDRAM空间地址配置如表6-4所示.

表6-3 存储器(SROM/SDRAM)地址引脚连接

表6-4 SDRAM空间地址配置

续表

6.1.4 nWAIT引脚功能

如果和每个地址空间相关联的WAIT被允许,某个地址空间处于激活状态的时候应该通过外部nWAIT引脚来延长nOE持续时间.从tacc-1核对nWAIT,在采样nWAIT为高电平的后一个时钟周期使nOE变为高电平,nWE信号和nOE信号相同.S3C2410A的外部nWAIT时序如图6-2所示.

图6-2 S3C2410A的外部nWAIT时序图(tacc=4)

6.1.5 nXBREQ/nXBACK引脚操作

如果nXBREQ被允许,处理器会在nXBACK引脚输出低电平作为应答信号,如果nXBACK引脚输出低电平,地址/数据总线和存储器控制信号会处于高阻状态,如图6-3所示.如果nXBREQ没有被允许,nXBACK也无效.

图6-3 S3C2410A的nXBREQ/nXBACK时序表

6.1.6 ROM接口

ROM接口举例如图6-4~图6-7所示.

图6-4 存储器与8bit ROM接口

图6-5 存储器与8bit ROM×2接口

图6-6 存储器与8bit ROM×4接口

图6-7 存储器与16bit ROM接口

6.1.7 SRAM存储器接口

SRAM存储器如图6-8、图6-9所示.

图6-8 存储器与16bit SRAM接口

图6-9 存储器与16bit SRAM×2接口

6.1.8 SDRAM接口

SDRAM接口举例如图6-10、图6-11所示.

图6-10 存储器与16bit SDRAM接口(8MB:1Mb×16×4banks)

图6-11 存储器与16bit SDRAM接口(16MB:1Mb×16×4banks×2ea)

6.1.9 可编程访问周期

可编程访问周期如图6-12、图6-13所示.

图6-12 S3C2410XnGCS时序图

图6-13 S3C2410XSDRAM时序图

6.1.10 存储器控制专用寄存器

(1)总线宽度/等待控制寄存器(BWSCON).

相关寄存器如下表所示.

表6-5 总线宽度/等待控制寄存器

寄存器各位功能:

[DWi]:i=0~7,其中DW0为只读,因为Bank0数据总线宽度在复位后已经由OM[1∶0]的电平决定.DW1~DW7可写,用于配置Bank1~Bank7的数据总线宽度,00表示8位数据总线宽度,01表示16位数据总线宽度,10表示32位数据总线宽度,11保留.

[WSi]:i=1~7,写入0则对应的Banki等待状态不使用,写入1则对应的Banki等待状态使能.

[STi]:i=1~7,决定SRAM是否使用UB/LB.0表示不使用UB/LB,引脚[14∶11]定义为nWBE[3∶0];1表示使用UB/LB,引脚[14∶11]定义为nBE[3∶0].

(2)Bank控制寄存器(BANKCONn:nGCS0-nGCS5).

相关寄存器如下表所示.

表6-6 Bank控制寄存器1

(3)Bank控制寄存器(BANKCONn:nGCS6-nGCS7).

相关寄存器如下表所示.

表6-7 Bank控制寄存器2

(4)刷新控制寄存器(REFRESH).

相关寄存器如下表所示.

表6-8 刷新控制寄存器

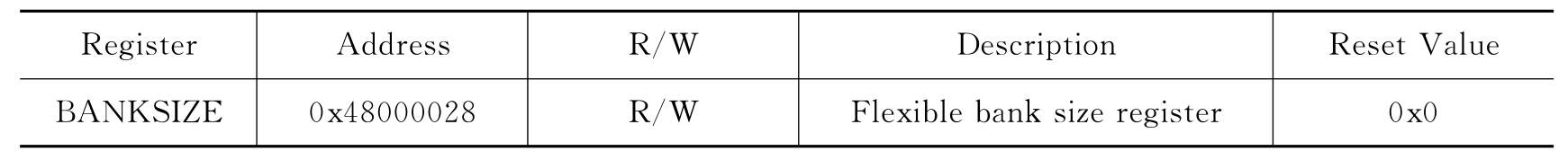

(5)Bank大小寄存器(BANKSIZE).

相关寄存器如下表所示.

表6-9 Bank大小寄存器

(6)SDRAM模式设置寄存器(MRSR).

相关寄存器如下表所示.

表6-10 SDRAM模式设置寄存器

以上所提到的寄存器的详细解释及设置请参考S3C2410数据手册.

下面列举了13个存储控制寄存器的配置示例:

BANKCON0_Val EQU 0x00000700

BANKCON1_Val EQU 0x00000700

BANKCON2_Val EQU 0x00000700

BANKCON3_Val EQU 0x00000700

BANKCON4_Val EQU 0x00000700

BANKCON5_Val EQU 0x00000700

BANKCON6_Val EQU 0x00018005

BANKCON7_Val EQU 0x00018005

BWSCON_Val EQU 0x22119120;0x22111110

REFRESH_Val EQU 0x008e0459

BANKSIZE_Val EQU 0x00000032;0x000000b2

MRSRB6_Val EQU 0x00000030

MRSRB7_Val EQU 0x00000030

观察上面寄存器介绍中的寄存器地址可以发现,13个寄存器分布在从0x48000000开始的连续地址空间,所以上面的程序可以利用指令"stmia r0,{r1-r13}"实现将配置好的CPU寄存器的值依次写入到相应的存储控制寄存器中.

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。