【摘要】:图7.5-10是由D触发器组成的3位数据寄存器。①存数过程:将输入的3位数据D3~D1同时加在触发器F3~F1的D输入端,在存数脉冲CP上升沿到来后,触发器被触发,使得3个D触发器的Q端状态保持为D3D2D1,完成了这3位数据的寄存;②取数过程:用3个“与”门来控制,取数脉冲到来之前,“与”门的输出Q3Q2Q1=000;取数脉冲到来时,各个“与”门将触发器的输出与“1”进行“与”运算,寄存在寄存器中的数据就被取出:Q3Q2Q1=D3D2D1。

7.5.4 数字寄存器

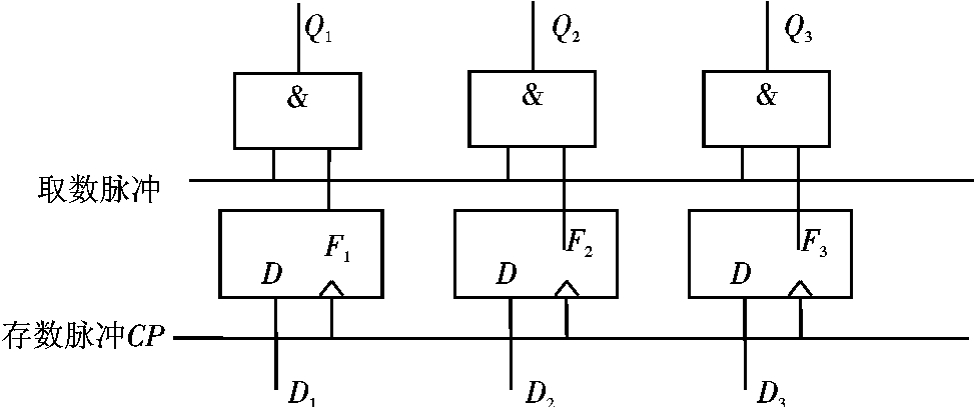

所谓寄存器是指能把二进制数据或代码暂时存储起来的电路。图7.5-10是由D触发器组成的3位数据寄存器。

该寄存器有存数和取数两个基本操作。

①存数过程:将输入的3位数据D3~D1同时加在触发器F3~F1的D输入端,在存数脉冲CP上升沿到来后,触发器被触发,使得3个D触发器的Q端状态保持为D3D2D1,完成了这3位数据的寄存;

②取数过程:用3个“与”门来控制,取数脉冲到来之前,“与”门的输出Q3Q2Q1=000;取数脉冲到来时,各个“与”门将触发器的输出与“1”进行“与”运算,寄存在寄存器中的数据就被取出:Q3Q2Q1=D3D2D1。

图7.5-10 3位数据寄存器

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。